Chip Gallery

A Batteryless Energy Harvesting Front-End for Powering Multiple IoT Nodes

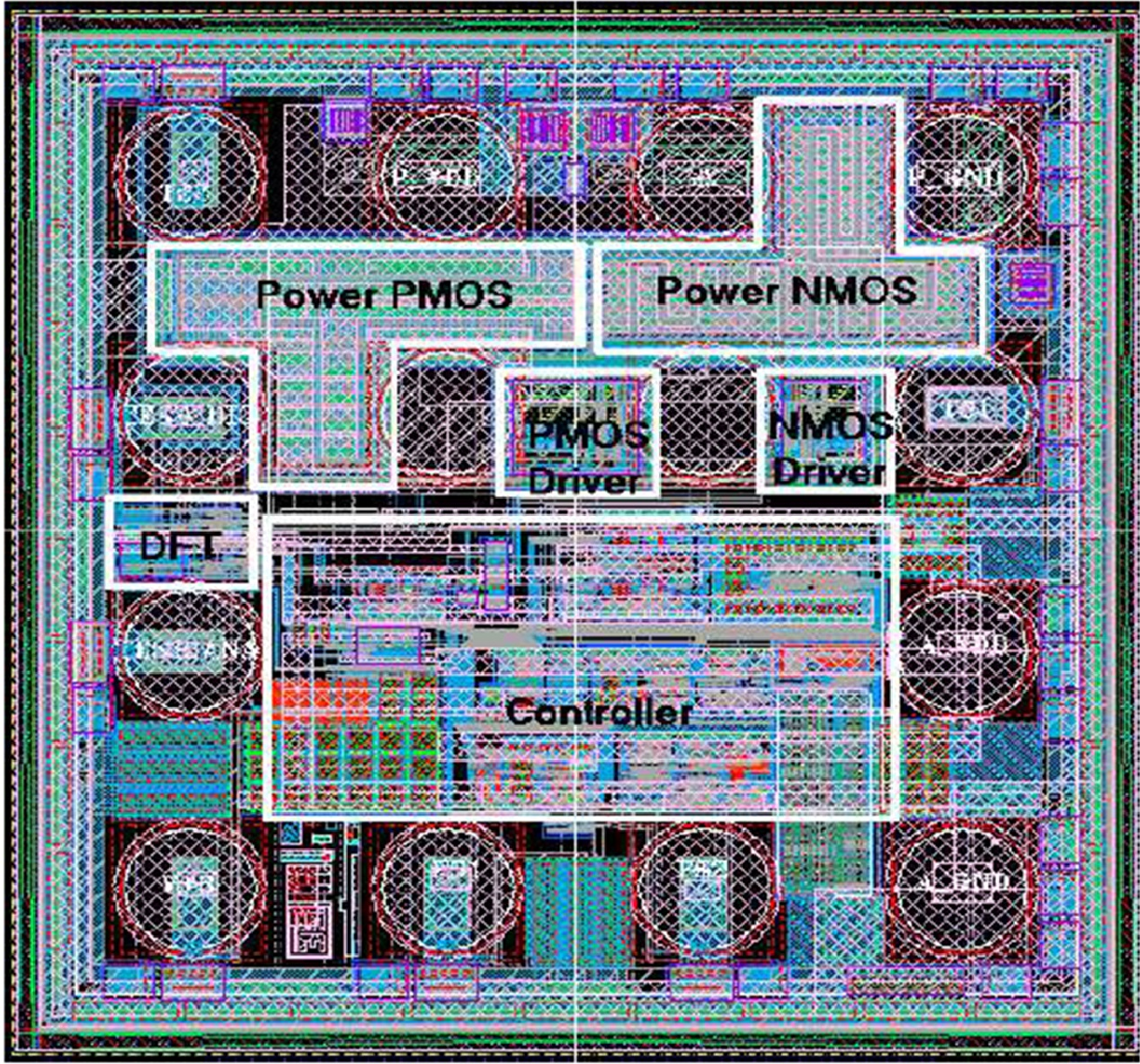

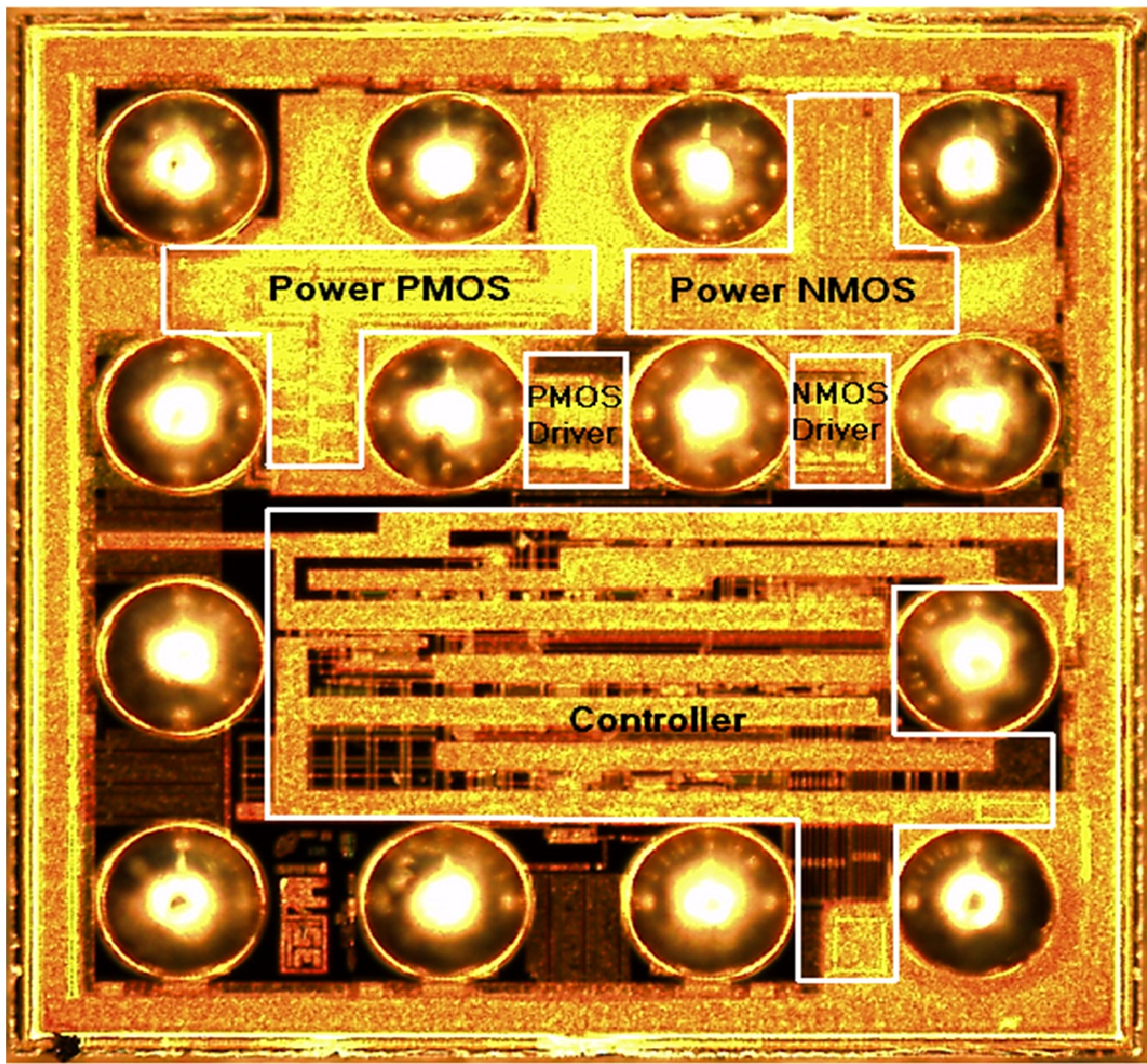

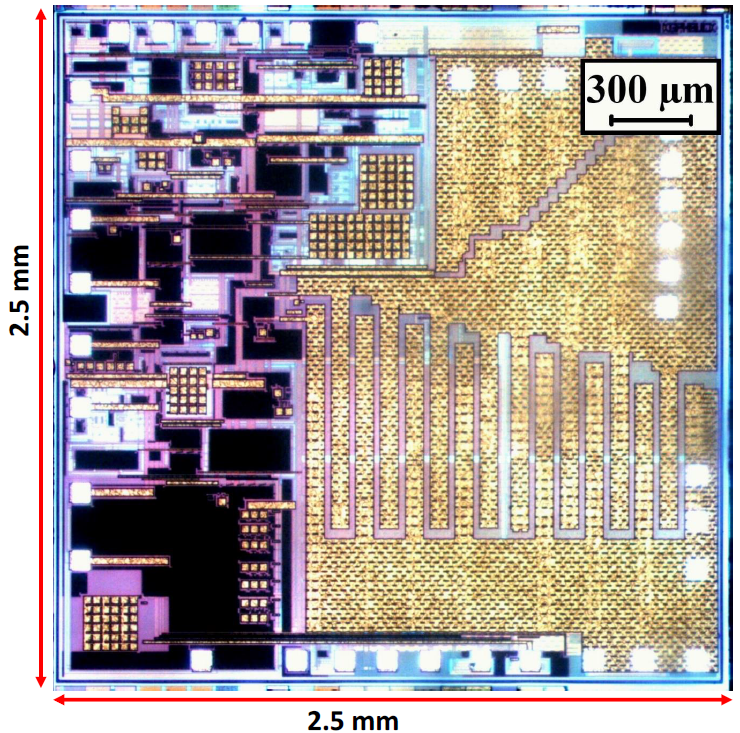

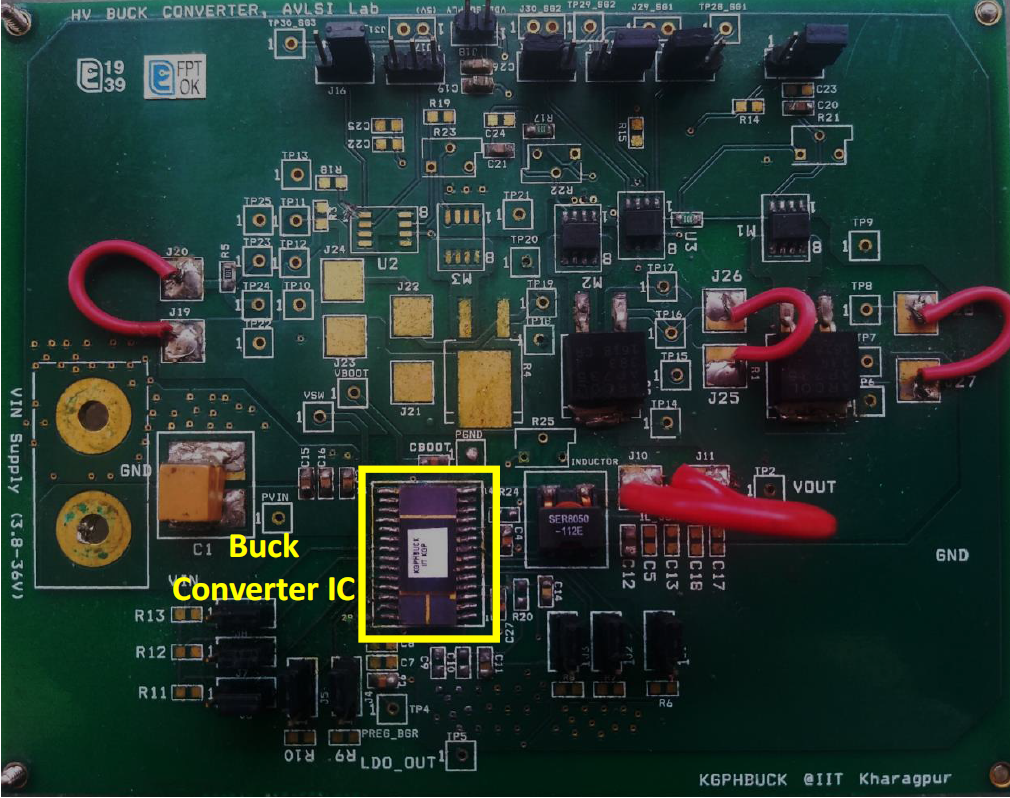

Design and Implementation of a Wide Input Voltage Buck Converter Chip for Automotive Applications

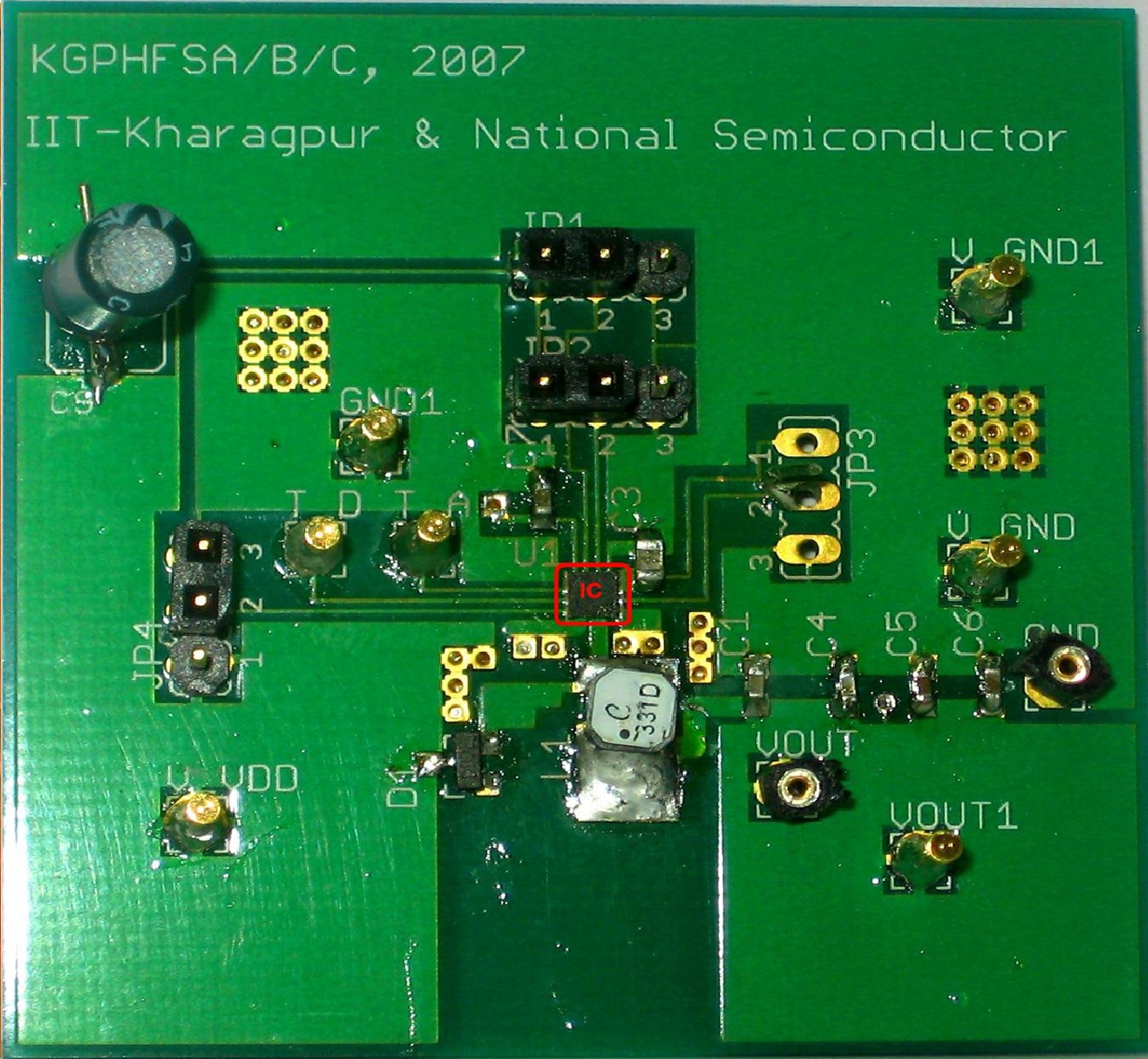

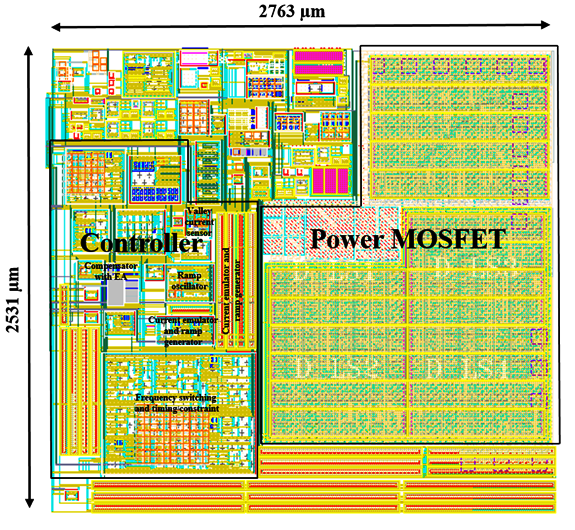

A Valley-Sensed Emulated Peak Current Controlled Buck Converter for Automotive Applications

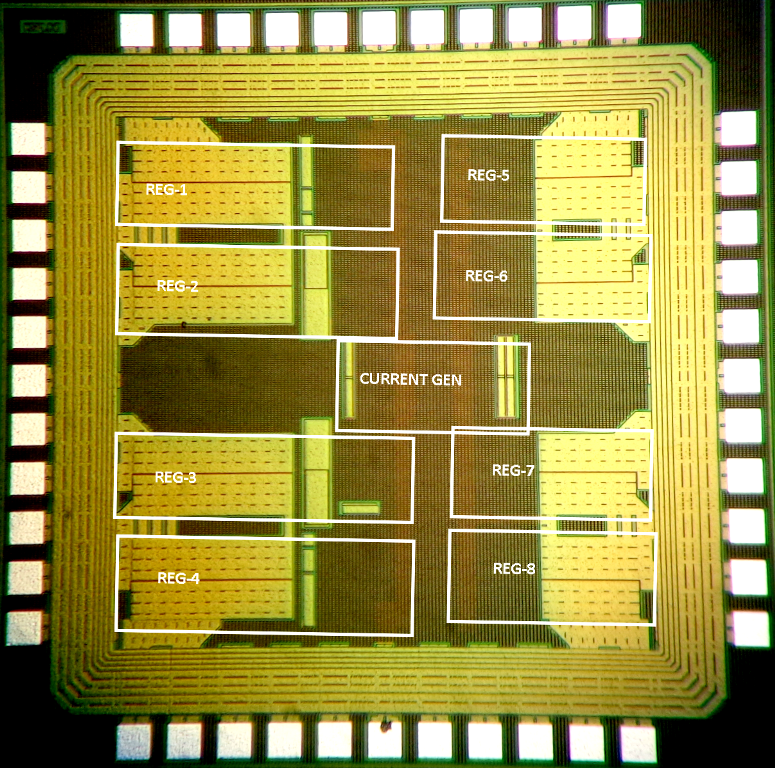

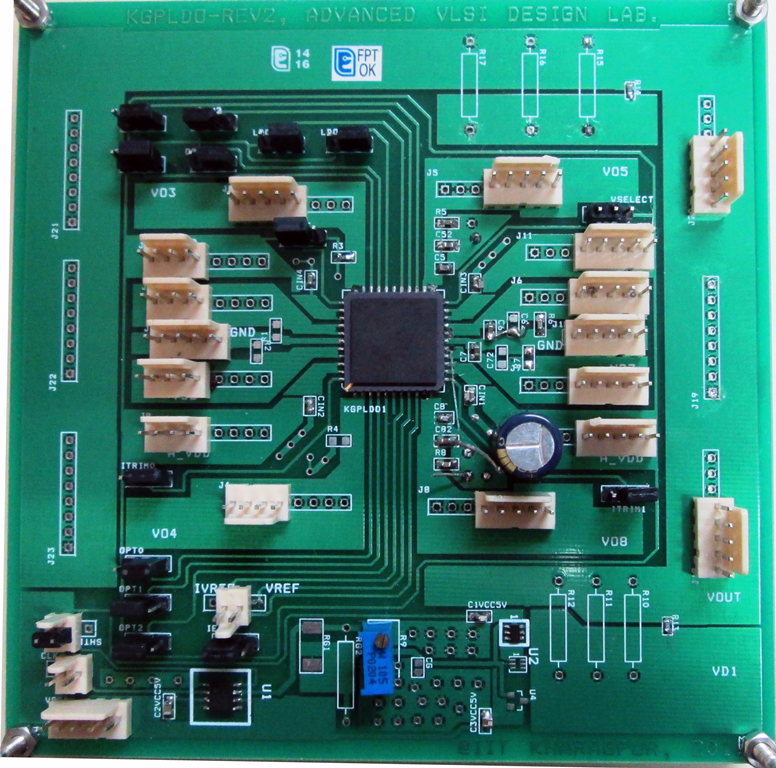

Design and Analysis of Self-Compensated Low Dropout Regulators

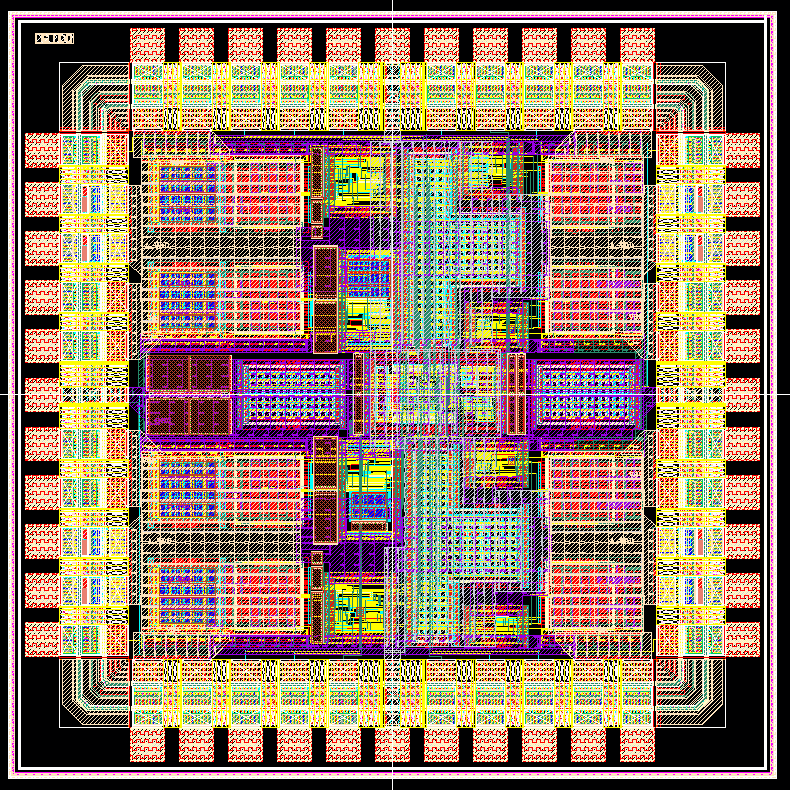

Design of a 20 MHz DC-DC Buck Converter with 84% Efficiency for Portable Applications