## Example 1 :: simple AND gate

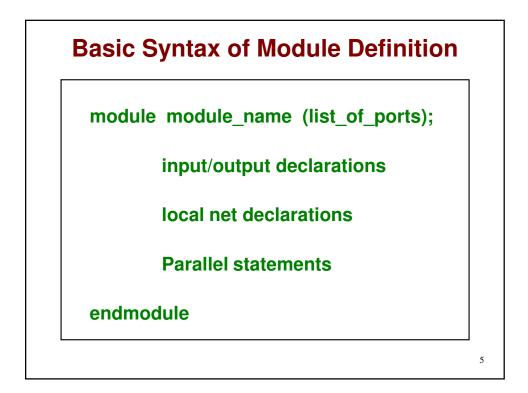

module simpleand (f, x, y);

input x, y;

output f;

assign f = x & y;

endmodule

## Example 2 :: two-level circuit

module two\_level (a, b, c, d, f); input a, b, c, d; output f; wire t1, t2; assign t1 = a & b; assign t2 =  $\sim$  (c | d); assign f = t1 ^ t2; endmodule

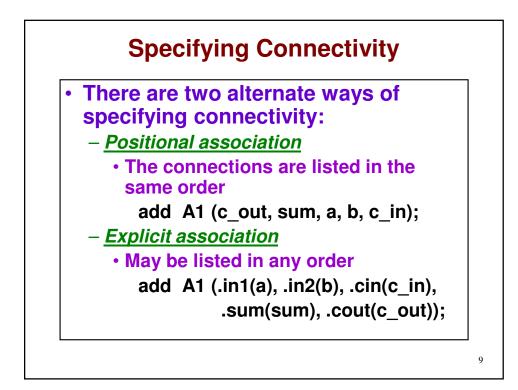

$\begin{array}{c} \mbox{Example 3 :: a hierarchical design} \\ \mbox{module add3 (s, cy3, cy_in, x, y);} \\ input [2:0] x, y; \\ input cy_in; \\ output cy_in; \\ output [2:0] s; \\ output cy3; \\ wire [1:0] cy_out; \\ add B0 (cy_out[0], s[0], x[0], y[0], cy_in); \\ add B1 (cy_out[1], s[1], x[1], y[1], cy_out[0]); \\ add B2 (cy3, s[2], x[2], y[2], cy_out[1]); \\ endmodule \\ \end{array}$

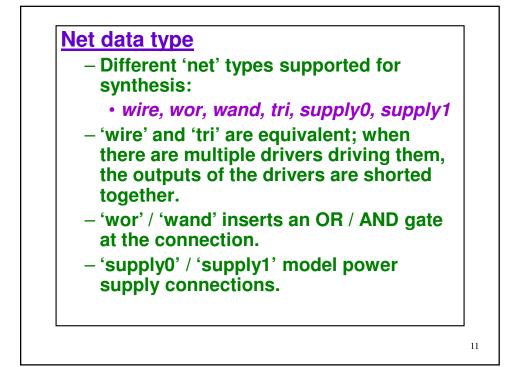

module using\_wire (A, B, C, D, f);

input A, B, C, D;

output f;

wire f; // net f declared as 'wire'

assign f = A & B;

assign f = C | D;

endmodule

```

module using_supply_wire (A, B, C, f);

input A, B, C;

output f;

supply0 gnd;

supply1 vdd;

nand G1 (t1, vdd, A, B);

xor G2 (t2, C, gnd);

and G3 (f, t1, t2);

endmodule

```

```

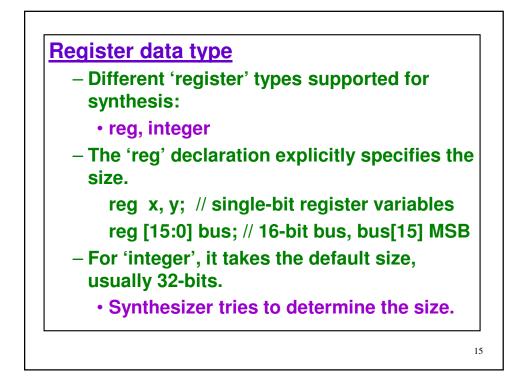

module simple_counter (clk, rst, count);

input clk, rst;

output count;

reg [31:0] count;

always @(posedge clk)

begin

if (rst)

count = 32'b0;

else

count = count + 1;

end

endmodule

```

```

// An 8-bit adder description

module parallel_adder (sum, cout, in1, in2, cin);

input [7:0] in1, in2; input cin;

output [7:0] sum; output cout;

assign #20 {cout, sum} = in1 + in2 + cin;

endmodule

```

```

// A combinational logic example

module mux21 (in1, in0, s, f);

input in1, in0, s;

output f;

reg f;

always @ (in1 or in0 or s)

if (s)

f = in1;

else

f = in0;

endmodule

```

```

// A sequential logic example

module dff_negedge (D, clock, Q, Qbar);

input D, clock;

output Q, Qbar;

reg Q, Qbar;

always @ (negedge clock)

begin

Q = D;

Qbar = ~D;

end

endmodule

```

```

// Another sequential logic example

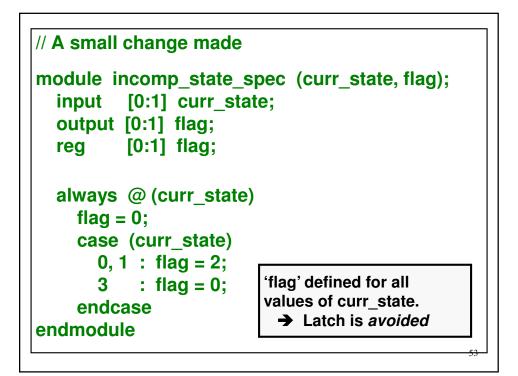

module incomp_state_spec (curr_state, flag);

input [0:1] curr_state;

output [0:1] flag;

[0:1] flag;

reg

always @ (curr_state)

case (curr_state)

0, 1 : flag = 2;

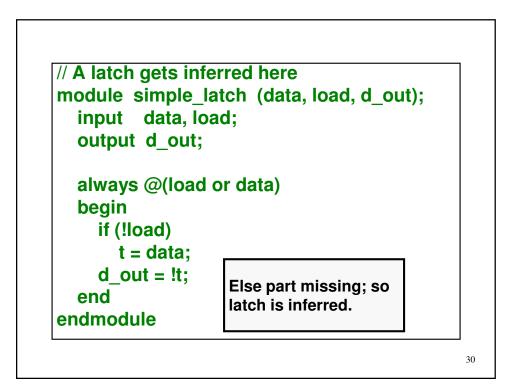

The variable 'flag' is not

3 : flag = 0;

assigned a value in all the

endcase

branches of case.

→ Latch is inferred

endmodule

```

```

\begin{array}{c} \mbox{module ALU_4bit (f, a, b, op);} \\ \mbox{input [1:0] op; input [3:0] a, b;} \\ \mbox{output [3:0] f; reg [3:0] f;} \\ \mbox{parameter ADD=2'b00, SUB=2'b01,} \\ \mbox{MUL=2'b10, DIV=2'b11;} \\ \mbox{always @ (a or b or op)} \\ \mbox{case (op)} \\ \mbox{ADD : f = a + b;} \\ \mbox{SUB : f = a - b;} \\ \mbox{MUL : f = a * b;} \\ \mbox{DIV : f = a / b;} \\ \mbox{endcase} \\ \mbox{endmodule} \end{array}

```

```

// Up-down counter (synchronous clear)

module counter (mode, clr, ld, d in, clk, count);

input mode, clr, ld, clk; input [0:7] d_in;

output [0:7] count;

reg [0:7] count;

always @ (posedge clk)

if (ld)

count \leq d in;

else if (clr)

count <= 0:

else if (mode)

count <= count + 1;

else

count <= count + 1;

endmodule

60

```

```

// Parameterized design:: an N-bit counter

module counter (clear, clock, count);

parameter N = 7;

input clear, clock;

output [0:N] count; reg [0:N] count;

always @ (negedge clock)

if (clear)

count <= 0;

else

count <= count + 1;

endmodule

```

```

// Using more than one clocks in a module

module multiple_clk (clk1, clk2, a, b, c, f1, f2);

input clk1, clk2, a, b, c;

output f1, f2;

reg f1, f2;

always @ (posedge clk1)

f1 <= a & b;

always @ (negedge clk2)

f2 <= b ^ c;

endmodule

```

```

// Using multiple edges of the same clock

module multi_phase_clk (a, b, f, clk);

input a, b, clk;

output f;

reg f, t;

always @ (posedge clk)

f <= t \& b;

always @ (negedge clk)

t <= a | b;

endmodule

```

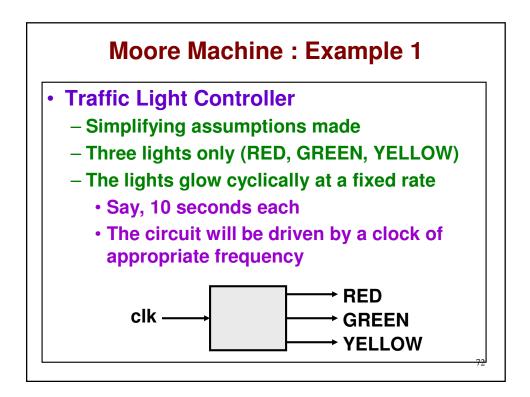

```

// S1 means YELLOW

S1: begin

light <= GREEN;

state <= S2;</pre>

end

// S2 means GREEN

S2: begin

light <= RED;</pre>

state <= S0;</pre>

end

default: begin

light <= RED;

state <= S0;</pre>

end

endcase

endmodule

74

```

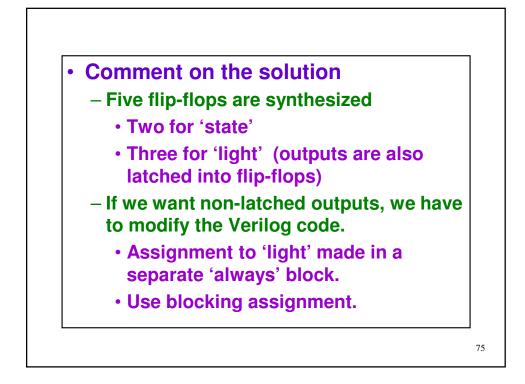

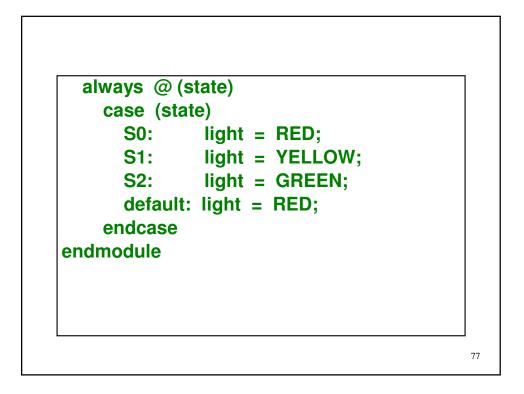

```

module traffic light nonlatched op (clk, light);

input clk;

output [0:2] light;

reg [0:2] light;

parameter S0=0, S1=1, S2=2;

parameter RED=3'b100, GREEN=3'b010,

YELLOW=3'b001;

reg [0:1] state;

always @ (posedge clk)

case (state)

state <= S1;

S0:

S1:

state <= S2;

S2:

state <= S0:

default: state <= S0;

endcase

```

```

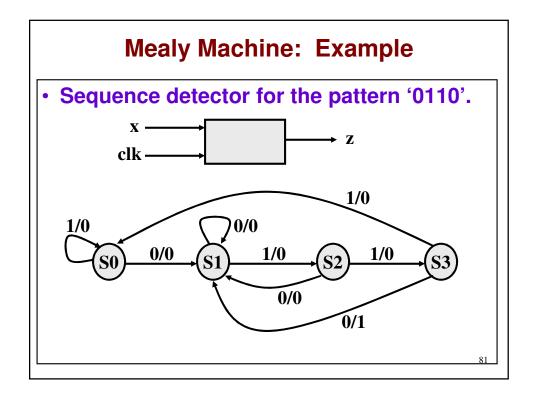

// Sequence detector for the pattern '0110'

module seq_detector (x, clk, z)

input x, clk;

output z; reg z;

parameter S0=0, S1=1, S2=2, S3=3;

reg [0:1] PS, NS;

always @ (posedge clk)

PS <= NS;</pre>

```

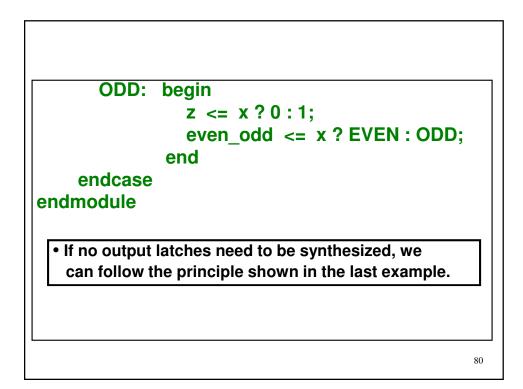

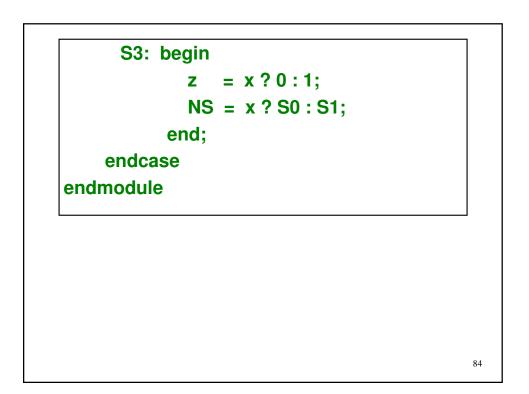

always @ (PS or x) case (PS) S0: begin z = x ? 0 : 0; NS = x ? S0 : S1; end; S1: begin z = x ? 0 : 0; NS = x ? S2 : S1; end; S2: begin z = x ? 0 : 0; NS = x ? S3 : S1; end;

```

module adder (sum, cy_out, in1, in2, cy_in);

input [7:0] in1, in2;

input cy_in;

output [7:0] sum; reg [7:0] sum;

output cy_out; reg cy_out;

always @ (in1 or in2 or cy_in)

{cy_out, sum} = in1 + in2 + cy_in;

endmodule

```

```

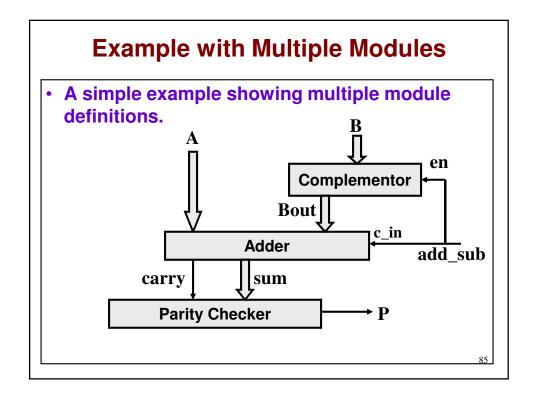

// Top level module

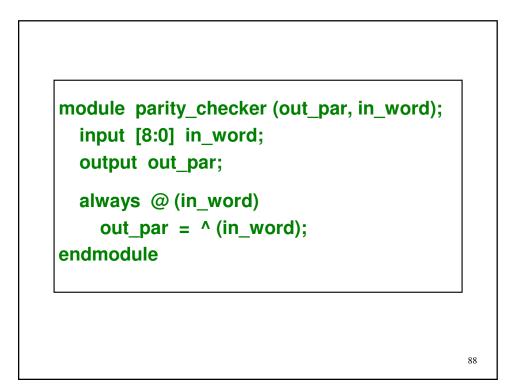

module add_sub_parity (p, a, b, add_sub);

input [7:0] a, b;

input add_sub; // 0 for add, 1 for subtract

output p; // parity of the result

wire [7:0] Bout, sum; wire carry;

complementor M1 (Bout, B, add_sub);

adder M2 (sum, carry, A, Bout, add_sub);

parity_checker M3 (p, {carry, sum});

endmodule

```

89

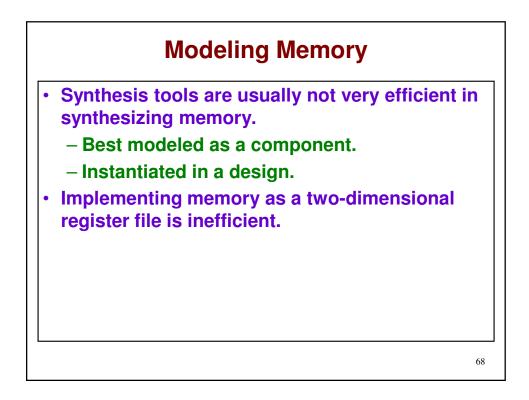

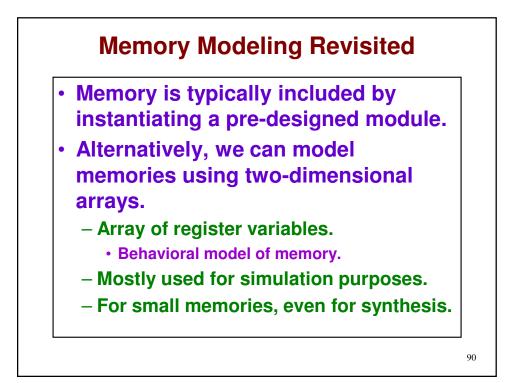

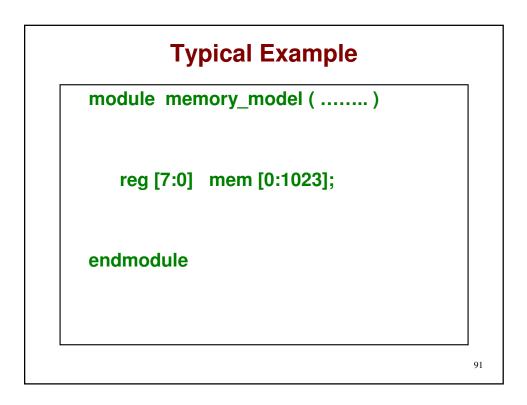

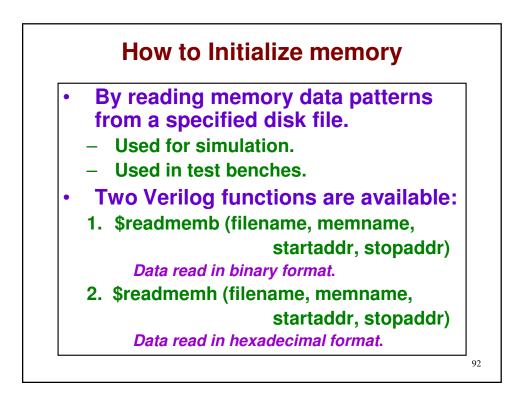

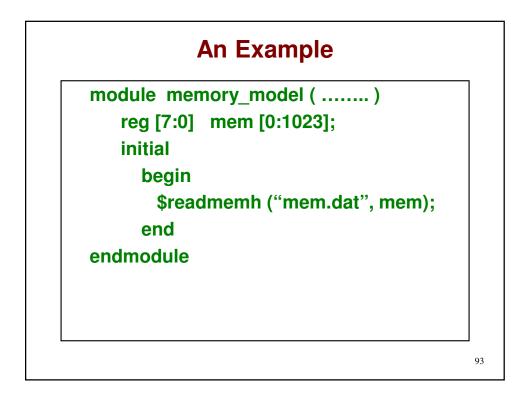

## A Specific Example :: Single Port RAM with Synchronous Read-Write

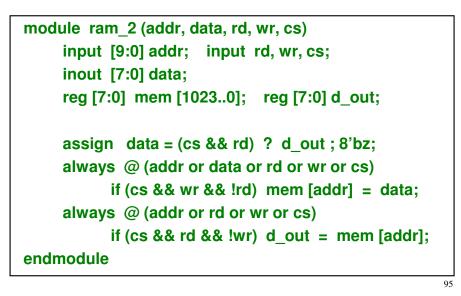

## A Specific Example :: Single Port RAM with Asynchronous Read-Write