## PSpice Assignments 1: Analog Signal Processing (EE60032),

Department of Electrical Engineering, Indian Institute of Technology, Kharagpur

Faculty: Ashis Maity Session: Autumn 2018

## Submission date: 7th August 2018

<u>Submission procedure:</u> Take the snapshot of the schematic and save the waveforms and prepare a word document. Add comments/discussion wherever required. The whole report should not exceed six pages. Submit the hard-copy/print-out version of the report.

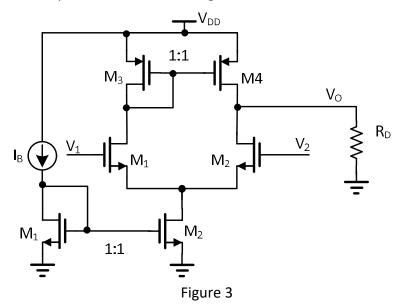

- 1. A current mirror circuit is shown in Figure 1 where  $I_{in}$ =100  $\mu$ A.

- a. Find out the threshold voltage of the transistors.

- b. If each transistor has W/L =  $10\mu m/0.5\mu m$ , measure the value of  $I_{out.}$

- c. After that, increase the transistor size  $100\mu m/5\mu m$  and measure the value of  $I_{out.}$

- d. Are there any differences you see in the results in step (b) and step (c)? Comment.

Figure 1

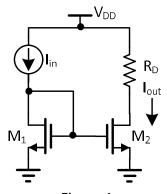

2. Design an NMOS differential pair with resistive load (shown in Figure 2) for a voltage gain of 50 and a power budget of 200  $\mu$ W subject to the condition that the stage following the differential pair an input CM level of at least 1.2V.

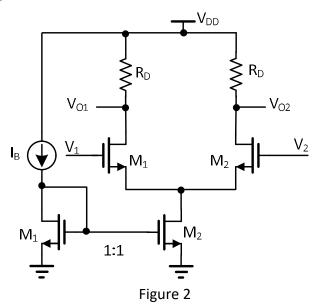

- 3. A differential amplifier with an active current mirror load (shown in Figure 3) has a tail bias current of 200  $\mu$ A. All the transistors have W/L = 20 $\mu$ m/0.4 $\mu$ m. Assume the input common mode voltage of 1.2 V and R<sub>L</sub>=10 k $\Omega$ .

- a. Find out the differential gain of the circuit.

- b. Find out the output common mode range.